SLIS031 - APRIL 1994 - REVISED JULY 1995

- Low r<sub>DS(on)</sub> . . . 5 Ω Typical

- Avalanche Energy . . . 30 mJ

- Eight Power DMOS-Transistor Outputs of 150-mA Continuous Current

- 500-mA Typical Current-Limiting Capability

- Output Clamp Voltage . . . 50 V

- Low Power Consumption

#### description

The TPIC6B273 is a monolithic, high-voltage, medium-current, power logic octal D-type latch with DMOS-transistor outputs designed for use in systems that require relatively high load power. The device contains a built-in voltage clamp on the outputs for inductive transient protection. Power driver applications include relays, solenoids, and other medium-current or high-voltage loads.

The TPIC6B273 contains eight positive-edgetriggered D-type flip-flops with a direct clear input. Each flip-flop features an open-drain power DMOS-transistor output.

When clear (CLR) is high, information at the D inputs meeting the setup time requirements is transferred to the DRAIN outputs on the positivegoing edge of the clock (CLK) pulse. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When the clock input (CLK) is at either the high or low level, the D input signal has no effect at the output. An asynchronous CLR is provided to turn all eight DMOS-transistor outputs off. When data is low for a given output, the DMOS-transistor output is off. When data is high, the DMOS-transistor output has sink-current capability.

Outputs are low-side, open-drain DMOS transistors with output ratings of 50 V and 150-mA continuous sink-current capability. Each output provides a 500-mA typical current limit at T<sub>C</sub> = 25°C. The current limit decreases as the junction temperature increases for additional device protection.

The TPIC6B273 is characterized for operation over the operating case temperature range of -40°C to 125°C.

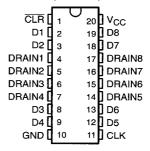

#### DW OR N PACKAGE (TOP VIEW)

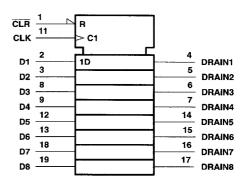

#### logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Standard 91-1984 and IEC Publication 617-12.

#### **FUNCTION TABLE** (each channel)

| INPUTS |          |   | OUTPUT  |

|--------|----------|---|---------|

| CLR    | CLK      | D | DRAIN   |

| L      | Х        | Х | H       |

| Н      | <b>↑</b> | Н | L       |

| Н      | <b>↑</b> | L | Н       |

| H      | L        | Х | Latched |

H = high level, L = low level, X = irrelevant

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include

Copyright @ 1995, Texas Instruments Incorporated

OST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

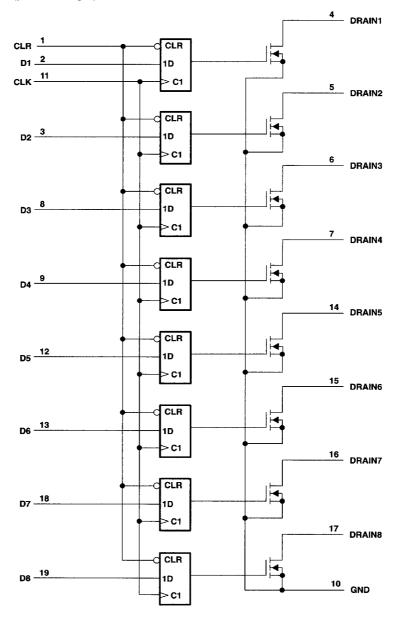

#### logic diagram (positive logic)

2-342

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

SLIS031 - APRIL 1994 - REVISED JULY 1995

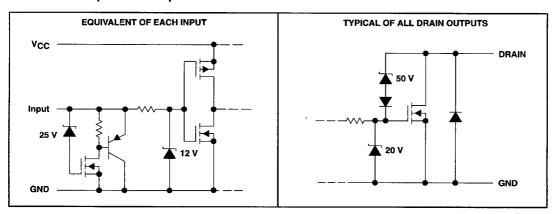

#### schematic of inputs and outputs

## absolute maximum ratings over recommended operating case temperature range (unless otherwise noted) $\!\!\!\!\!^{\dagger}$

| Logic supply voltage, V <sub>CC</sub> (see Note 1)                                    | 7 V          |

|---------------------------------------------------------------------------------------|--------------|

| Logic input voltage range, V <sub>1</sub>                                             | 0.3 V to 7 V |

| Power DMOS drain-to-source voltage, V <sub>DS</sub> (see Note 2)                      | 50 V         |

| Continuous source-to-drain diode anode current                                        | 500 mA       |

| Pulsed source-to-drain diode anode current (see Note 3)                               |              |

| Pulsed drain current, each output, all outputs on, ID, TC = 25°C (see Note 3)         | 500 mA       |

| Continuous drain current, each output, all outputs on, $I_D$ , $T_C = 25^{\circ}C$    | 150 mA       |

| Peak drain current single output, I <sub>DM</sub> ,T <sub>C</sub> = 25°C (see Note 3) |              |

| Single-pulse avalanche energy, EAS (see Figure 4)                                     |              |

| Avalanche current, I <sub>AS</sub> (see Note 4)                                       | 500 mA       |

| Continuous total dissipation                                                          |              |

| Operating virtual junction temperature range, T <sub>J</sub>                          |              |

| Operating case temperature range, T <sub>C</sub>                                      |              |

| Storage temperature range                                                             |              |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                          | 260°C        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to GND.

- 2. Each power DMOS source is internally connected to GND.

- 3. Pulse duration  $\leq$  100  $\mu$ s and duty cycle  $\leq$  2%.

- 4. DRAIN supply voltage = 15 V, starting junction temperature (T<sub>JS</sub>) = 25°C, L = 200 mH, I<sub>AS</sub> = 0.5 A (see Figure 4).

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>C</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>C</sub> = 25°C | T <sub>C</sub> = 125°C<br>POWER RATING |

|---------|---------------------------------------|------------------------------------------------|----------------------------------------|

| DW      | 1389 mW                               | 11.1 mW/°C                                     | 278 mW                                 |

| N       | 1050 mW                               | 10.5 mW/°C                                     | 263 mW                                 |

# TPIC6B273 POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 - APRIL 1994 - REVISED JULY 1995

#### recommended operating conditions

|                                                                                               | MIN                  | MAX                   | UNIT |

|-----------------------------------------------------------------------------------------------|----------------------|-----------------------|------|

| Logic supply voltage, VCC                                                                     | 4.5                  | 5.5                   | ٧    |

| High-level input voltage, VIH                                                                 | 0.85 V <sub>CC</sub> |                       | ٧    |

| Low-level input voltage, V <sub>I</sub> L                                                     |                      | 0.15 V <sub>C</sub> C | ٧    |

| Pulsed drain output current, T <sub>C</sub> = 25°C, V <sub>CC</sub> = 5 V (see Notes 3 and 5) | -500                 | 500                   | mA   |

| Setup time, D high before CLK↑, t <sub>SU</sub> (see Figure 2)                                | 20                   |                       | ns   |

| Hold time, D high after CLK↑, th (see Figure 2)                                               | 20                   |                       | ns   |

| Pulse duration, t <sub>W</sub> (see Figure 2)                                                 | 40                   |                       | ns   |

| Operating case temperature, T <sub>C</sub>                                                    | -40                  | 125                   | °C   |

#### electrical characteristics, $V_{CC} = 5 \text{ V}$ , $T_{C} = 25^{\circ}\text{C}$ (unless otherwise noted)

| PARAMETER            |                                            | TEST CONDITIONS                                    |                                  |                                          | MIN     | TYP  | MAX | UNIT |

|----------------------|--------------------------------------------|----------------------------------------------------|----------------------------------|------------------------------------------|---------|------|-----|------|

| V <sub>(BR)DSX</sub> | Drain-to-source breakdown voltage          | I <sub>D</sub> = 1 mA                              |                                  |                                          | 50      |      |     | ٧    |

| V <sub>SD</sub>      | Source-to-drain diode forward voltage      | I <sub>F</sub> = 100 mA                            |                                  |                                          |         | 0.85 | 1   | ٧    |

| lН                   | High-level input current                   | V <sub>CC</sub> = 5.5 V,                           | V <sub>I</sub> = V <sub>CC</sub> |                                          |         |      | 1   | μA   |

| I <sub>IL</sub>      | Low-level input current                    | V <sub>CC</sub> = 5.5 V,                           | V <sub>I</sub> = 0               |                                          | ·       |      | -1  | μА   |

|                      |                                            | V <sub>CC</sub> = 5.5 V                            | All outputs off                  |                                          |         | 20   | 100 |      |

| Icc                  | Logic supply current                       |                                                    | All outputs on                   |                                          | 150 300 |      | 300 | μА   |

| IN                   | Nominal current                            | V <sub>DS(on)</sub> = 0.5 V,<br>See Notes 5, 6, a  |                                  | T <sub>C</sub> = 85°C,                   |         | 90   |     | mA   |

|                      | 0" 11 11 11                                | V <sub>DS</sub> = 40 V,                            | V <sub>CC</sub> = 5.5 V          |                                          |         | 0.1  | 5   |      |

| DSX                  | Off-state drain current                    | V <sub>DS</sub> = 40 V,                            | V <sub>CC</sub> = 5.5 V,         | T <sub>C</sub> = 125°C                   |         | 0.15 | 8   | μА   |

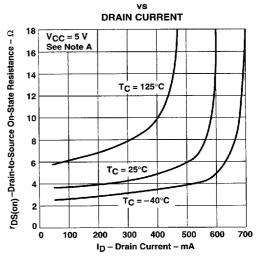

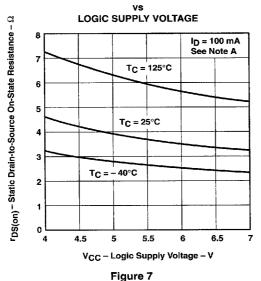

|                      |                                            | I <sub>D</sub> = 100 mA,                           | V <sub>CC</sub> = 4.5 V          |                                          |         | 4.2  | 5.7 |      |

| rDS(on)              | Static drain-to-source on-state resistance | I <sub>D</sub> = 100 mA,<br>T <sub>C</sub> = 125°C | V <sub>CC</sub> = 4.5 V,         | See Notes 5 and 6<br>and Figures 6 and 7 |         | 6.8  | 9.5 | Ω    |

|                      |                                            | I <sub>D</sub> = 350 mA,                           | V <sub>CC</sub> = 4.5 V          | 1                                        |         | 5.5  | 8   |      |

#### switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_{C} = 25^{\circ}\text{C}$

| PARAMETER        |                                                           | TEST CONDITIONS                                  | MIN | TYP | MAX | UNIT |  |

|------------------|-----------------------------------------------------------|--------------------------------------------------|-----|-----|-----|------|--|

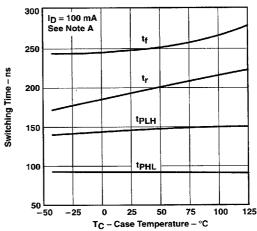

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level output from CLK |                                                  | 150 |     | ns  |      |  |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level output from CLK | C <sub>1</sub> = 30 pF, I <sub>D</sub> = 100 mA, | 90  |     | ns  |      |  |

| tr               | Rise time, drain output                                   | See Figures 1, 2, and 8                          |     | 200 |     | ns   |  |

| tf               | Fall time, drain output                                   |                                                  |     | 200 |     | ns   |  |

| ta               | Reverse-recovery-current rise time                        | l <sub>F</sub> = 100 mA, di/dt = 20 A/μs,        |     | 100 |     |      |  |

| trr              | Reverse-recovery time                                     | See Notes 5 and 6 and Figure 3                   |     | 300 |     | ns   |  |

NOTES: 3. Pulse duration  $\leq$  100  $\mu$ s and duty cycle  $\leq$  2%.

- 5. Technique should limit T<sub>J</sub> T<sub>C</sub> to 10°C maximum.

- 6. These parameters are measured with voltage-sensing contacts separate from the current-carrying contacts.

- Nominal current is defined for a consistent comparison between devices from different sources. It is the current that produces a voltage drop of 0.5 V at T<sub>C</sub> = 85°C.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SLIS031 - APRIL 1994 - REVISED JULY 1995

#### thermal resistance

| PARAMETER         |                                         | TEST CONDITIONS | MIN                            | MAX | UNIT |      |

|-------------------|-----------------------------------------|-----------------|--------------------------------|-----|------|------|

| R <sub>0</sub> JA | Thermal resistance, junction-to-ambient | DW package      | All 8 outputs with equal power |     | 90   | °C/W |

|                   |                                         | N package       | All 8 outputs with equal power |     | 95   |      |

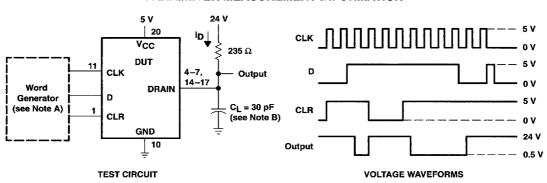

#### PARAMETER MEASUREMENT INFORMATION

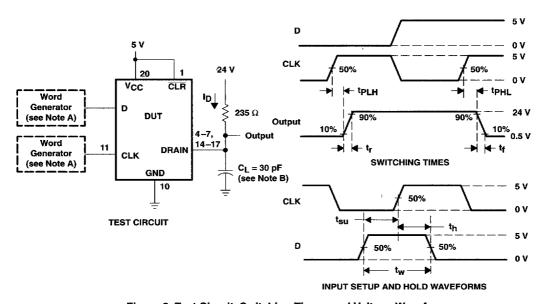

Figure 1. Resistive-Load Test Circuit and Voltage Waveforms

Figure 2. Test Circuit, Switching Times, and Voltage Waveforms

NOTES: A. The word generator has the following characteristics:  $t_f \le 10$  ns,  $t_f \le 10$  ns,  $t_w = 300$  ns, pulsed repetition rate (PRR) = 5 KHz,  $Z_O = 50 \Omega$

B. CL includes probe and jig capacitance.

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

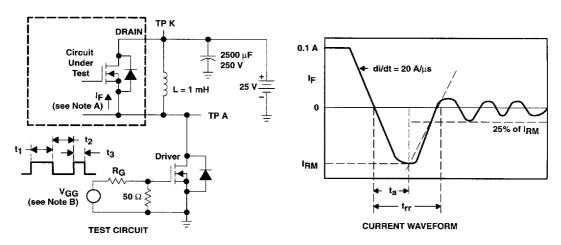

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. The DRAIN terminal under test is connected to the TP K test point. All other terminals are connected together and connected to the TP A test point.

- B. The VGG amplitude and RG are adjusted for di/dt = 20 A/ $\mu$ s. A VGG double-pulse train is used to set IF = 0.1 A, where t<sub>1</sub> = 10  $\mu$ s, t<sub>2</sub> = 7  $\mu$ s, and t<sub>3</sub> = 3  $\mu$ s.

Figure 3. Reverse-Recovery-Current Test Circuit and Waveforms of Source-to-Drain Diode

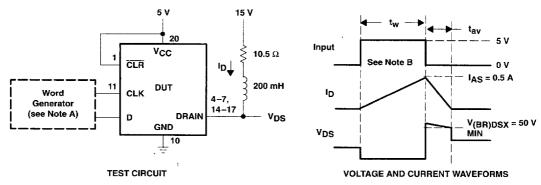

- NOTES: A The word generator has the following characteristics:  $t_{\Gamma} \le 10$  ns,  $t_{\Gamma} \le 10$  ns,  $t_{\Omega} = 50 \Omega$

- B. Input pulse duration,  $t_W$ , is increased until peak current  $I_{AS} = 0.5$  A. Energy test is defined as  $E_{AS} = I_{AS} \times V_{(BR)DSX} \times t_{av}/2 = 30$  mJ

Figure 4. Single-Pulse Avalanche Energy Test Circuit and Waveforms

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

#### TYPICAL CHARACTERISTICS

# TIME DURATION OF AVALANCHE TO TC = 25°C TO

Figure 5

#### **DRAIN-TO-SOURCE ON-STATE RESISTANCE**

Figure 6

#### STATIC DRAIN-TO-SOURCE ON-STATE RESISTANCE

NOTE C. Technique should limit  $T_J - T_C$  to 10°C maximum.

# SWITCHING TIME vs CASE TEMPERATURE 300 ID = 100 mA See Note A

Figure 8

| 8961724 0100934 126 |

POST DESIGN BOY 655303 • DALLAS TEXAS 75265

#### THERMAL INFORMATION

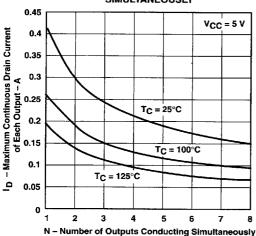

# MAXIMUM CONTINUOUS DRAIN CURRENT OF EACH OUTPUT vs

### NUMBER OF OUTPUTS CONDUCTING SIMULTANEOUSLY

Figure 9

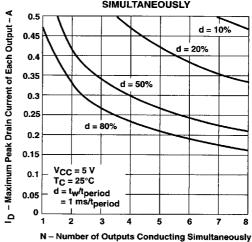

#### MAXIMUM PEAK DRAIN CURRENT OF EACH OUTPUT

# NUMBER OF OUTPUTS CONDUCTING SIMULTANEOUSLY

Figure 10

POST OFFICE BOX 655303 ● DALLAS, TEXAS 752